概述

触发器组成的寄存器是存储少量数据的存储器,而存储器阵列,可以存储电路使用、生成的大量数据。

概念

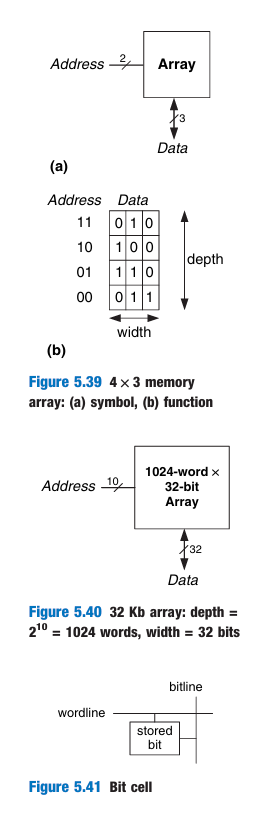

- 地址:存储器可以写入内容到阵列的一行。每一行由地址指定。

- 字:读出或写入的值被称为数据,每行数据有 M 位,称为一个字。

- 深度、宽度:

- 深度是行数,为地址数,N 位地址有 行;

- 宽度为列数,是字的位数,M 位数据有 M 列。

- 阵列大小(容量):,这样的阵列包括了 depth 个 width 位字(字单元),称为 阵列。特别的,可以进行二维存储,每行多个字,由行列地址指定具体单元,例如:, 字线,M 位线。

- 性能指标:

- 访问时间 :随机访问存储器,指读或写操作所用时间;其他类型,指将读写机构定位到目标位置所需的时间。

- 存储周期 : 仅对RAM而言,指两次访问存储单元间的最小时间间隔。

- 带宽/数据传输率:

- 一般的随机访问存储器:

- 其他类型:,带宽:

- :读写N bits所需的平均时间

- :访问时间

- :N bits

- :存储部件的数据传输率(bits/s)

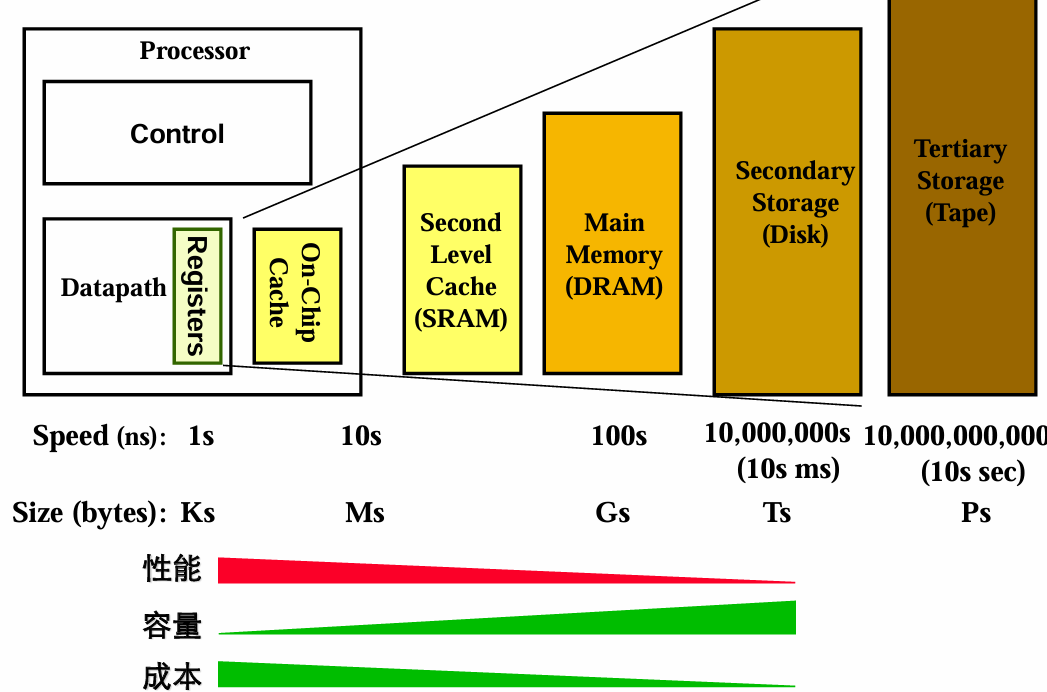

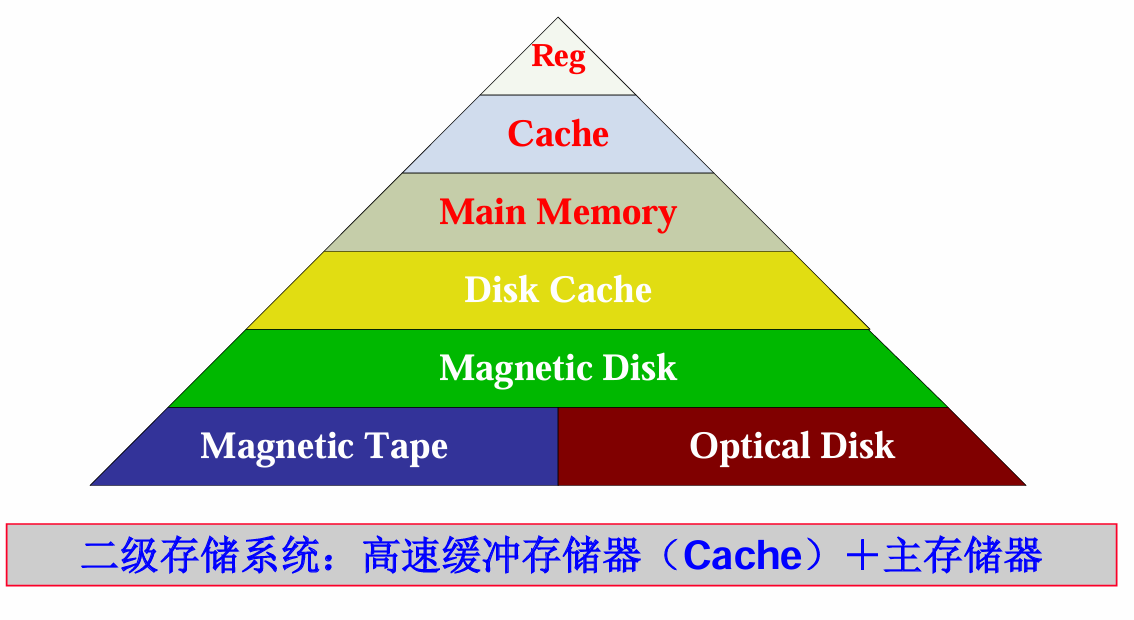

- 性能/层次特征:

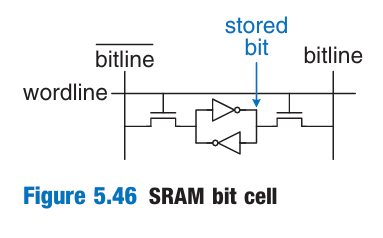

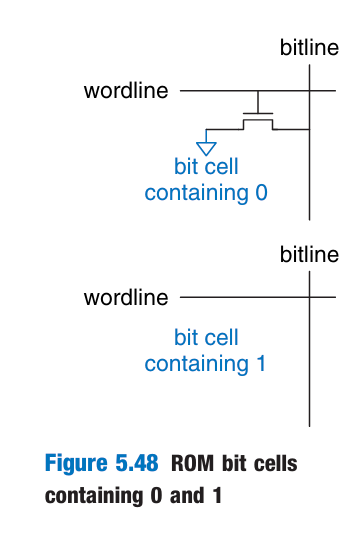

位单元

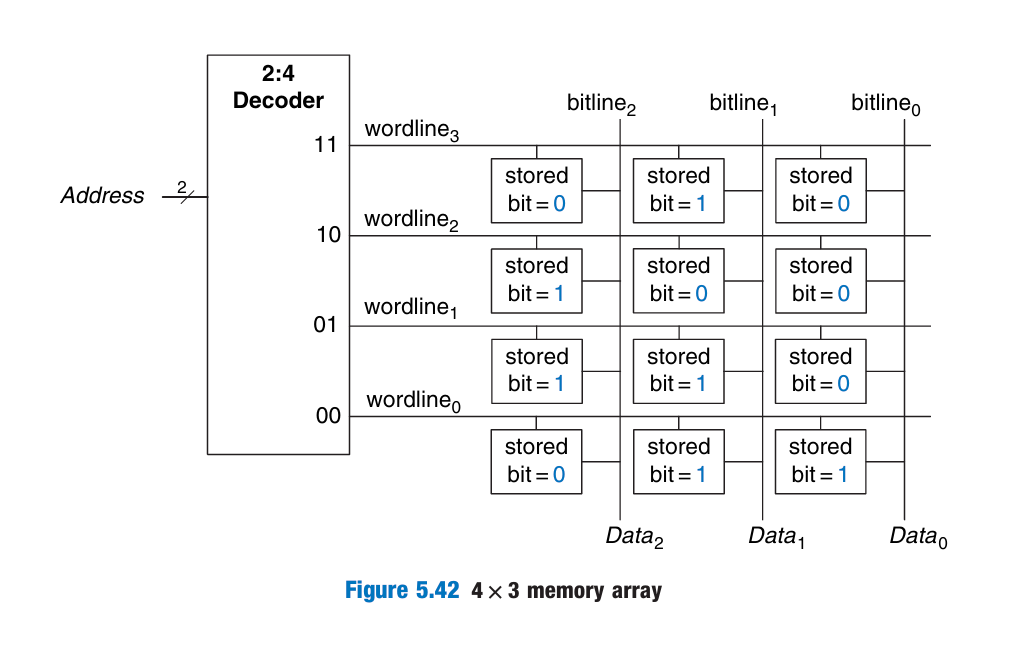

- 概念:存储器阵列由位单元的阵列组成,每个位单元存储一位数据。

- 组成:一个位单元与一个字线和一个位线连接。

- 字线:对于每一个地址位组合,存储器把字线设为高电位,激活此行。

- 位线:字线为高电平时,位线传输要读或存的位,否则与位单元断开,为浮空值。

存储器的结构

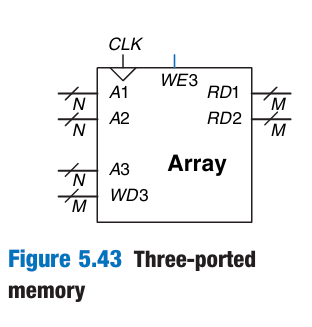

存储器端口

多端口存储器可以同时访问多个地址,详细可查看设计文档。

种类

存储器可以根据其如何在位单元上存储位来分类。

- 随机访问存储器(RAM)

- 特点:易失(断电丢失数据)

- 分类:

- 动态 RAM(DRAM):电容充放电存储数据

- 静态 RAM(SRAM):交叉耦合反相器存储数据

- 只读存储器(ROM)

- 特点:非易失(无电源也可无期限保存数据)

- 分类:根据擦写方式不同有很多类型

易失与否是它们本质的区别,因为大多数现代 ROM 可以读也可以写。

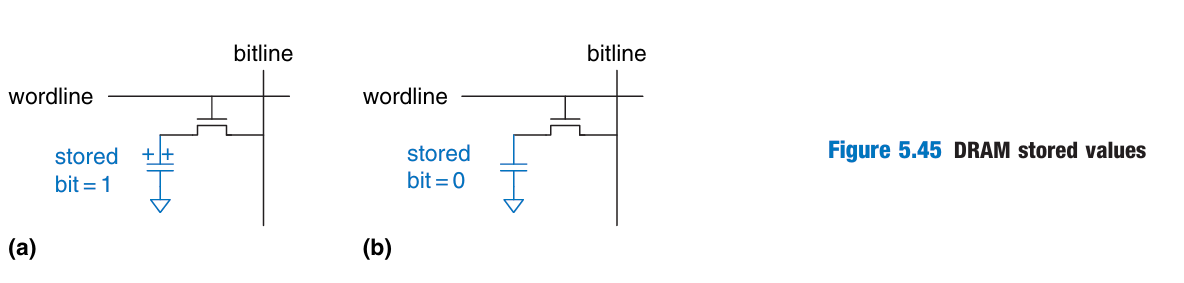

DRAM

- 存储方式:以电容充放电存储位。

- 特点:

- 读破坏电容中的位值,每次读后要重写数据。即使没有被读也要刷新(读、重写)

- 按行刷新、所有芯片同时进行,刷新操作与CPU访问内存分开进行

- 刷新地址计数器和复用器选择输入读写地址或者刷新地址

- DRAM的读过程就是对原来保存信息的读取、放大、再写入的过程

- 用途:主存储器

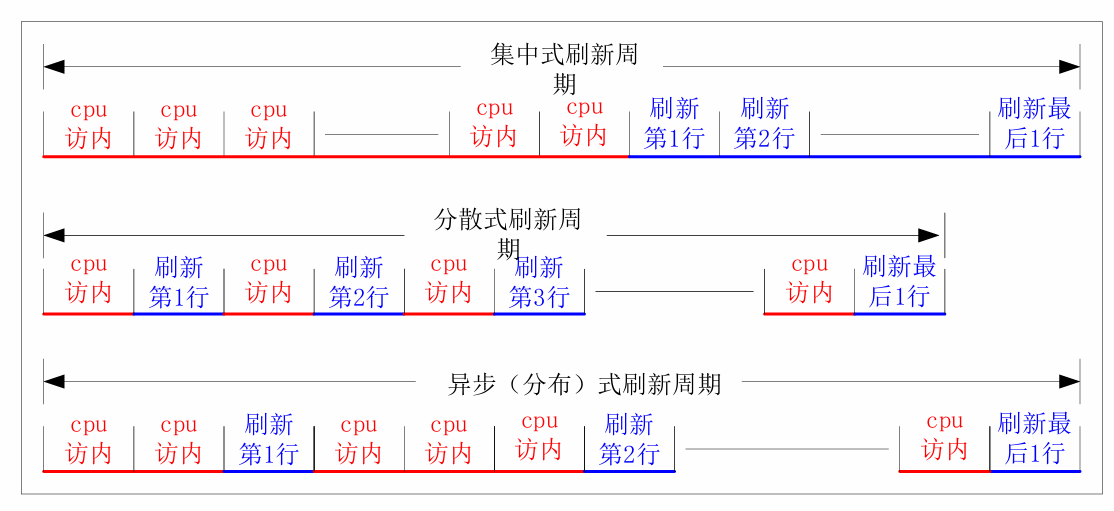

- 刷新方式:

- 集中式:将刷新周期分成两部分,在一个时间段内,刷新存储器所有行,此时CPU停止访问内存;另一个时间段内, CPU可以访问内存,刷新电路不工作。

- 存在死区时间,即集中刷新的时间,此时不能读写

- 刷新间隔 = 刷新周期

- 分散式:CPU与刷新电路交替访问内存,一个存储周期刷新1行,下一个存储周期刷新另一行,直至最后1行后,又开始刷新第1行。

- 使系统速度降低,但不存在停止读写操作的死区时间

- 刷新间隔 = 刷新行数 * 存储周期 刷新周期

- 分布式:保证在一个刷新周期内,将存储芯片内的所有行刷新一遍,两次刷新操作之间,可能等时间间距,也可能不等。

- 是前两种的结合,可减少死区时间,同时保证性能

- 刷新间隔 = 刷新周期

- 集中式:将刷新周期分成两部分,在一个时间段内,刷新存储器所有行,此时CPU停止访问内存;另一个时间段内, CPU可以访问内存,刷新电路不工作。

SRAM

- 存储方式:交叉耦合反相器

- 特点:不需要刷新存储位。有两个输出: 和 。

- 用途:Cache

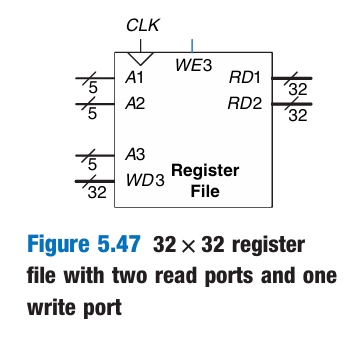

寄存器文件

数字系统常用一组寄存器存储临时变量,称为寄存器文件。通常由小型多端口 SRAM 阵列组成,比触发器阵列更紧凑。

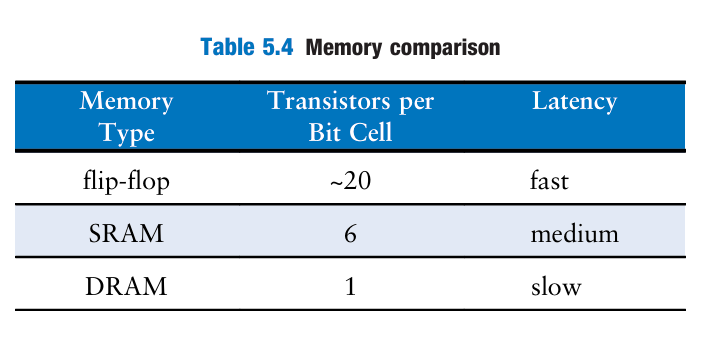

面积与延迟

同为易失的存储器,触发器、SRAM 和 DRAM 在成本(晶体管数目)和延迟上各有优劣。

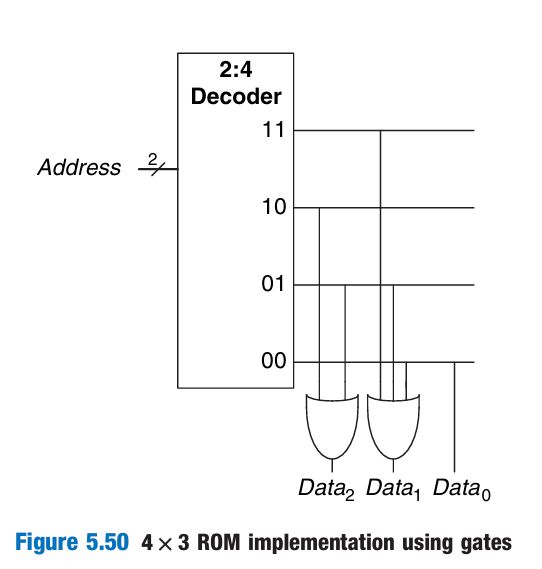

ROM

- 存储方式:晶体管的存在与否决定为 0 或 1。

- 特点:

- 位单元是组合电路,可以用一组 AND 门(构成一个译码器)后跟一组 OR 门的 2 级逻辑组成。

- 现代 ROM 可写入,写入时间更长但非易失。

可以用点表示法表示,行为字线、列为位线,交叉有点为 1,否则为 0。

可以用逻辑电路表示:

- 类别:

- 可编程 ROM(PROM):每个位单元都放置一个晶体管,提供方法决定是否接地。

- 熔丝烧断可编程 ROM:使用者通过高电压选择性熔断熔丝来对 ROM 编程。熔丝存在则接地为 0,否则为 1。(一次可编程)

- 可擦除 PROM(EPROM)、电子可擦除 PROM(EEPROM)、flash

- 可编程 ROM(PROM):每个位单元都放置一个晶体管,提供方法决定是否接地。

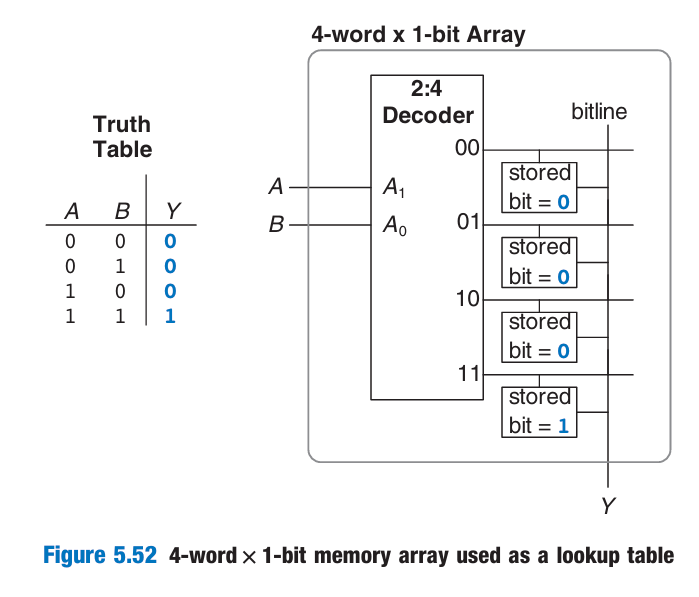

存储器阵列逻辑

存储器也可以实现组合逻辑功能。一个 的存储器可以实现任意的 N 输入、M 输出的组合逻辑功能。

这被称为查找表(LUT)

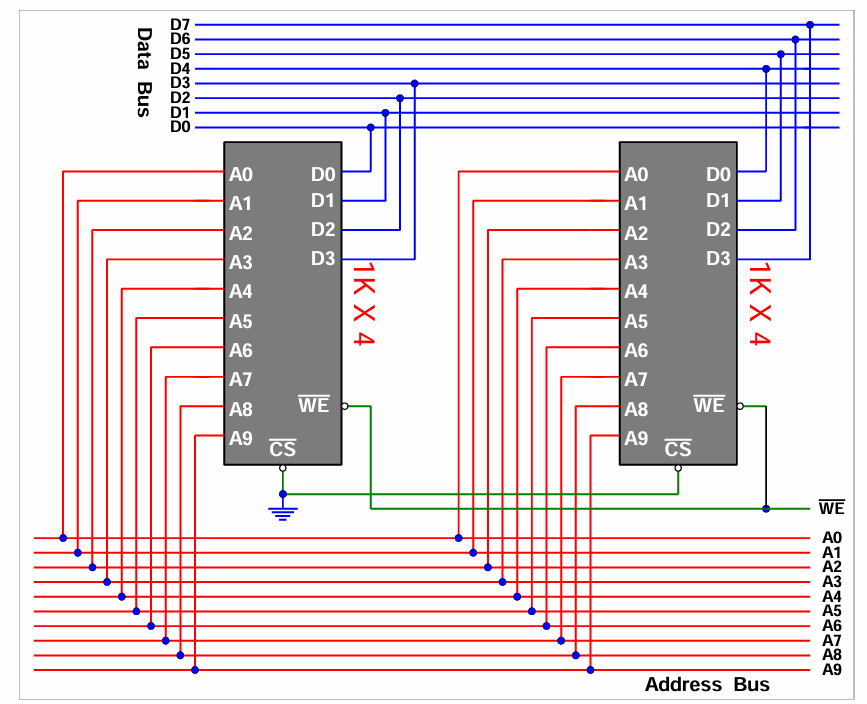

存储器芯片扩展

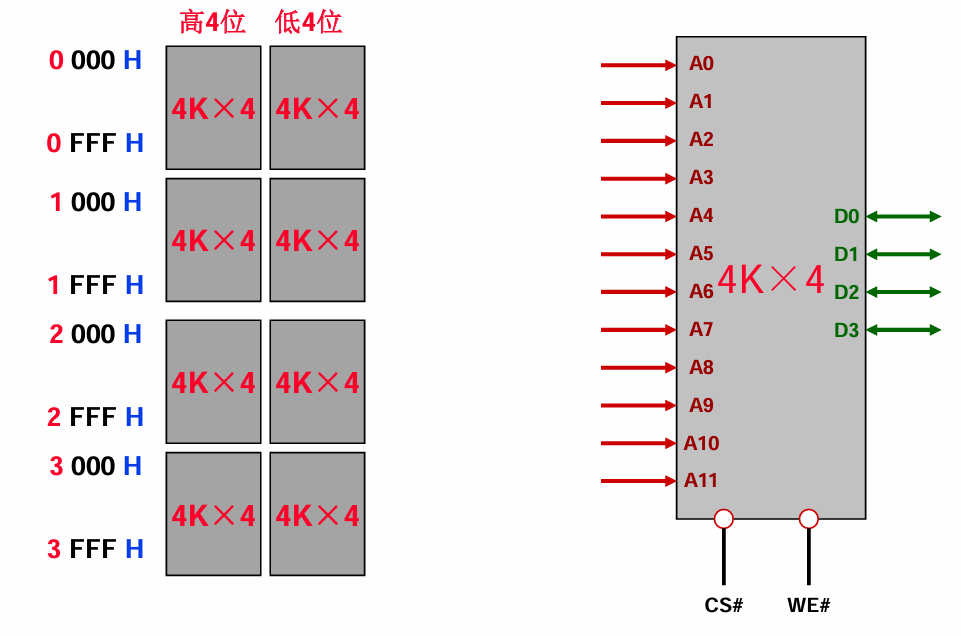

位扩展

- 本质:增大 M(width)

- 原因:芯片中存储字单元的数量足够,但字单元的位数不足。

- 方法:多个存储器芯片的数据位空间拼在一起。

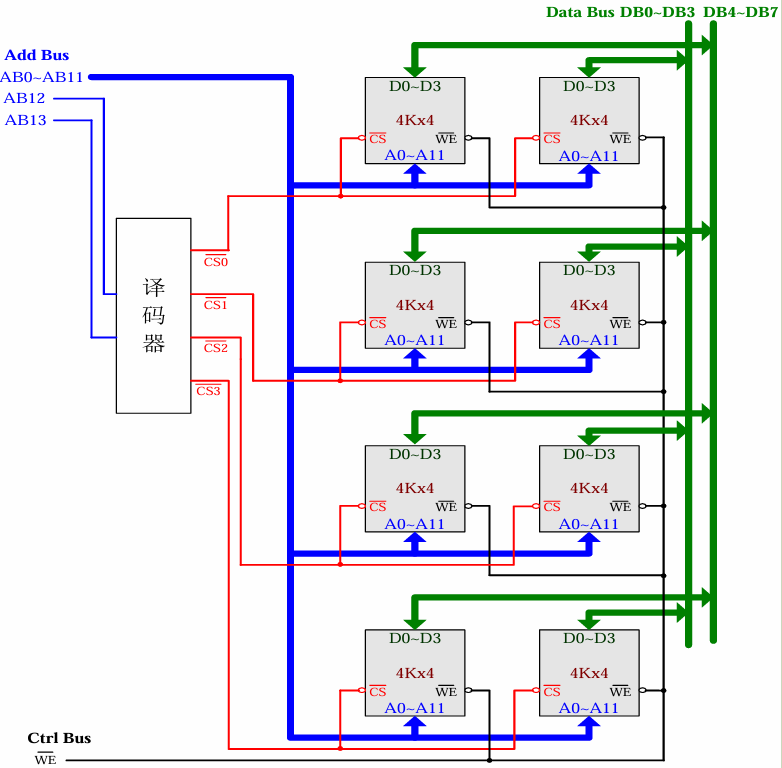

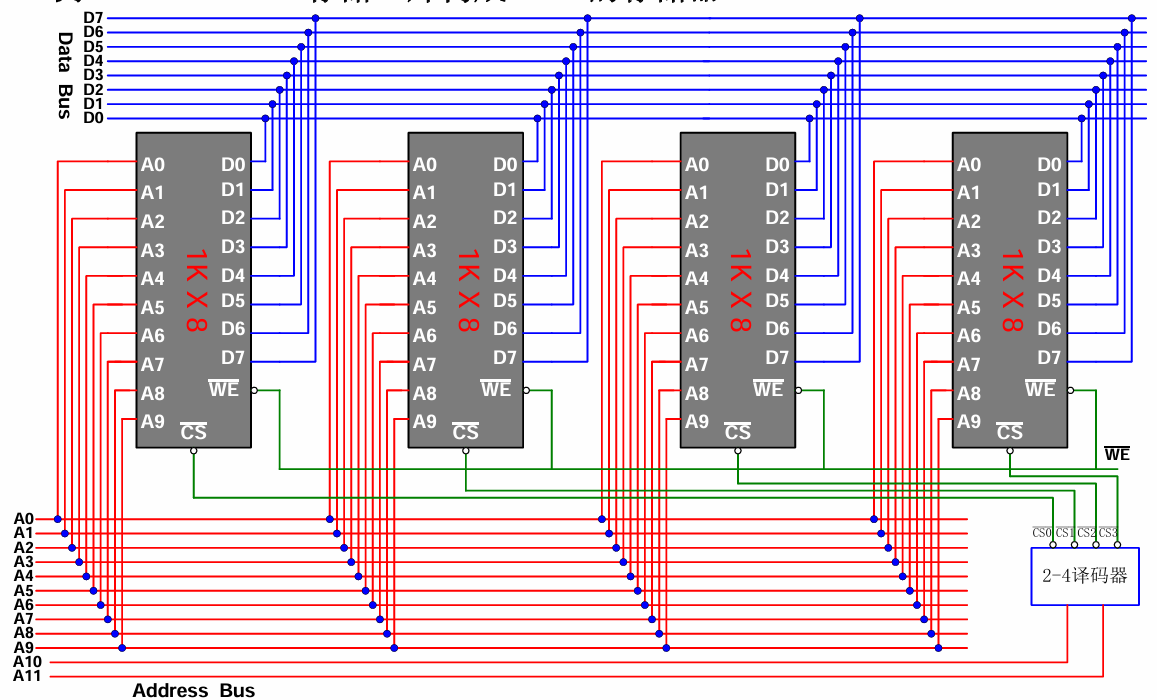

字扩展

- 本质:增大 N(depth)

- 原因:存储器芯片存储字数量不足,地址有剩余;存储字单元的数据位数足够。

- 方法:多个存储器芯片的地址空间拼在一起。关键在于,把高位地址作为片选的编码。

混合扩展

- 本质:同时增大 N(depth)和 M(width)

- 原因:存储器芯片存储字数量和每个子单元的位数均不足。

- 方法:综合应用位扩展和字扩展。