时序电路

时序电路包括所有不是组合电路的电路,输出不能简单根据当前输入确定,会包含环路,可能发生竞争等。

锁存器:电位触发

结构基础

- 交叉耦合反相器

- N种稳态的元件可以表示log N位信息,双稳态原件为1种,etc

- 对于双稳态,若Q已知,~Q已知,因此虽然有两个节点,但只有一个信息,可以用任意一个。

- 没有控制状态的输入

SR

- 结构:交叉耦合或非门(高有效)、交叉耦合与非门(低有效)

- 输入:S(set)、R(reset)

- 输出:Q、~Q

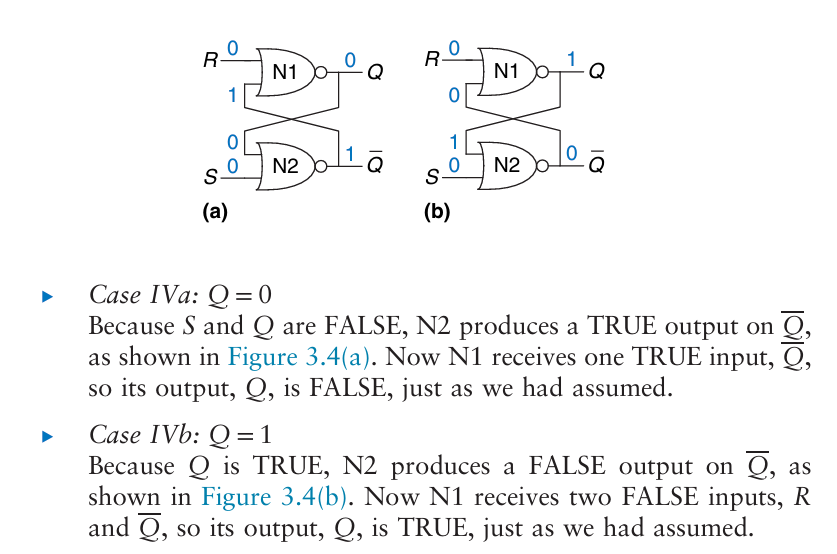

接下来以 NOR 型为例:

R = S = 0时,输出保持初值不变;Set将Q置1,Reset将Q置0。

- 真值表:

| S | R | Q | ~Q |

|---|---|---|---|

| 0 | 0 | Qprev | ~Qprev |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 |

- 输出由S、R决定,S、R 不同时为 1(非法)。

- 特征方程:

给 NOR 型的信号,取反后再给 NAND 型,逻辑输出一致。但是时序等会有不同。

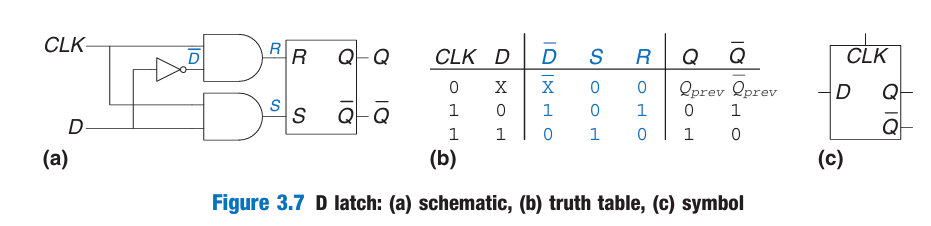

D

- 输入:

- D(data):控制下一个状态的值

- CLK(clock):控制状态发生改变的时间

- 输出:Q,~Q

- CLK = 0时,不透明,Q保持不变;CLK = 1时,透明,Q置为D。

- 特征方程: 时钟有效时

- 优点:

- 分离了内容与时间,知道了改变为什么、何时改变。

- 可以让锁存器在时钟信号下同步工作,是电位触发的锁存器,即同步锁存器。

- S、R 总是互非(合并为 ),防止非法状态。

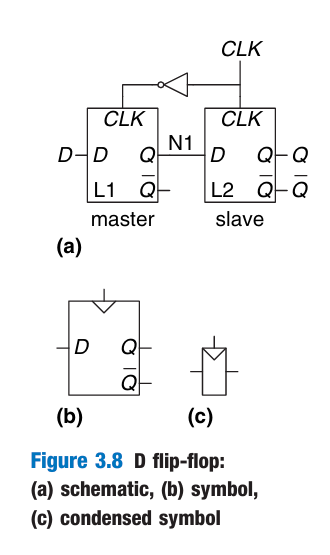

触发器:边沿触发

D

- 组成:由反向时钟控制的两个背靠背D锁存器,一主一从

- 功能:D触发器在时钟上升/下降沿(时钟沿)将D复制到Q(采样),在其余时间保持原有状态

- 因此相比D锁存器,D锁存器在 CLK 高电平时一直透明,D触发器仅在边沿更新值。

- 边沿触发类型:

- 正沿触发

posedge:Master 在上升沿关闭,也即 Master 接入 - 负沿触发

negedge:Master 在下降沿关闭,也即 Master 接入

- 正沿触发

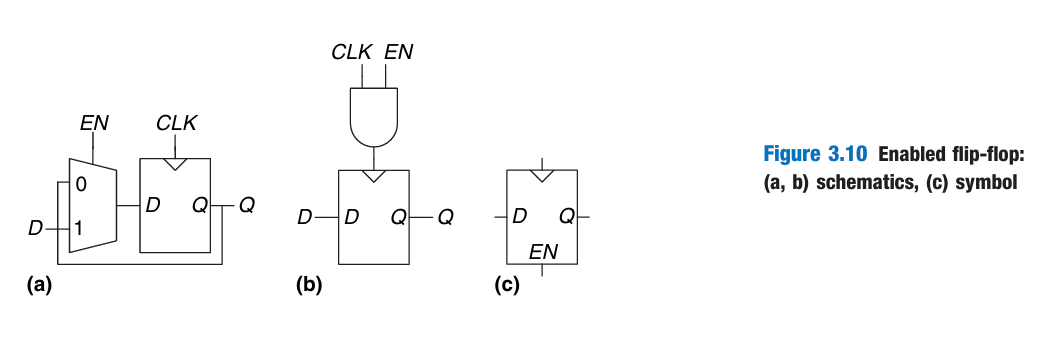

- 使能信号:

事实上,a 是更好的选择。在时钟信号上一般不要设置逻辑,否则可能因延迟导致时序错误。

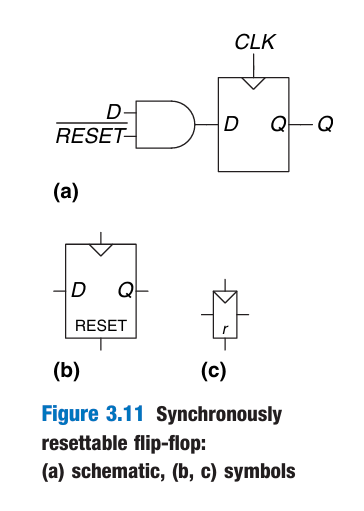

- (同步)复位信号:

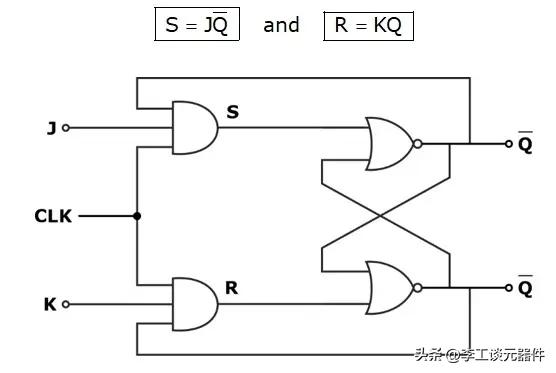

JK

- 特点:没有非法输入。两输入 J,K 都为 1 时为翻转。

- 真值表:

| J | K | Q |

|---|---|---|

| 0 | 0 | |

| 0 | 1 | 0 |

| 1 | 0 | 1 |

| 1 | 1 |

- 电路图:

- 特征方程:时钟有效时

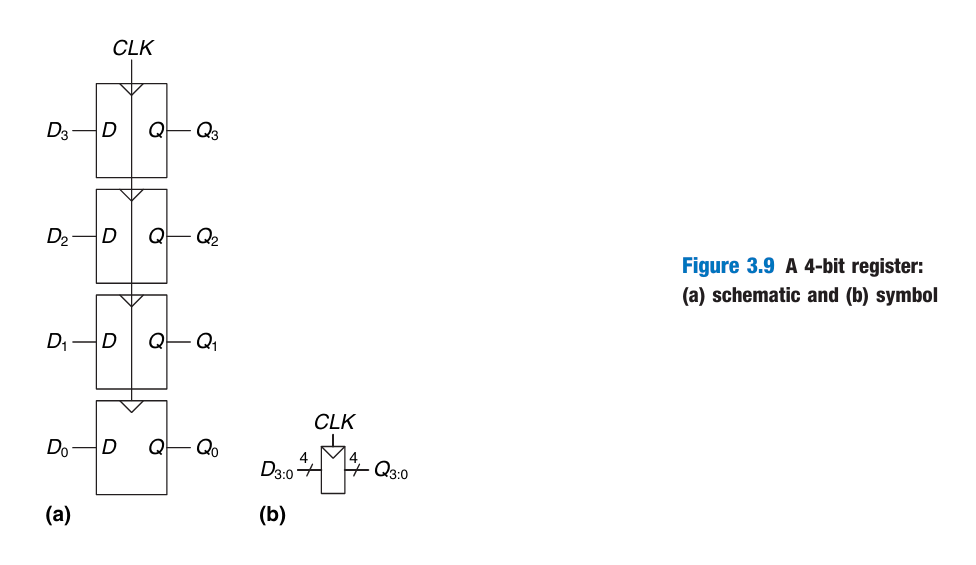

寄存器

- 组成:一个 N 位寄存器由共享一个公共 CLK 输入的 N 个触发器组成(寄存器所有位同时被更新)

移位寄存器

- 特点:每来一个时钟脉冲,寄存器中数据就依次向左或向右移一位。

- 工作方式:

- 串入并出:串并转换

- 串入串出:数据延迟(延迟线)

- 并入串出:并串转换

- 并入并出:数据预置

计数器

- 分类:

- 同步:所有触发器的时钟端并联在一起,同时翻转。

- 异步(串行):输入系统时钟脉冲只作用于最低位触发器,高位触发器的时钟信号往往是由低一位触发器的输出提供的。设计简单。

- 加法:上升沿触发器: ,下降沿触发器:)。

- 减法:与加法相反。

同步逻辑设计

同步时序电路

包含环路的时序电路存在不良竞争或不稳定行为,设计师用寄存器来断开环路,转化为组合逻辑电路与寄存器的集合。

定义

- 输入:一组有限离散状态+时钟输入(上升沿表示电路状态发生改变的时间)

- 功能规范:当前状态与输入值的各种组合,输出和下一个状态的值

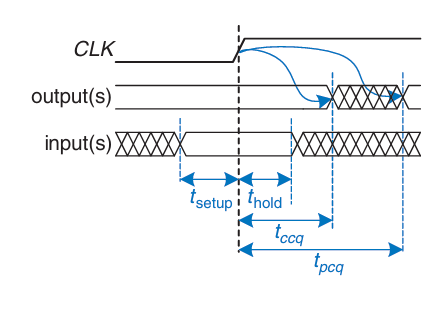

- 时序规范:传播延迟(tpcq)、最小延迟(tccq)(这两个从时钟沿开始计时,是触发器的传播延迟与最小延迟)、孔径时间(时钟上升沿直到输出改变的时间以及建立时间tsetup、保持时间thold)→ 输入必须相对于时钟上升沿稳定。

特点

寄存器+组合电路,环路有寄存器

常见同步时序电路

- 有限状态机

- 流水线

有限状态机

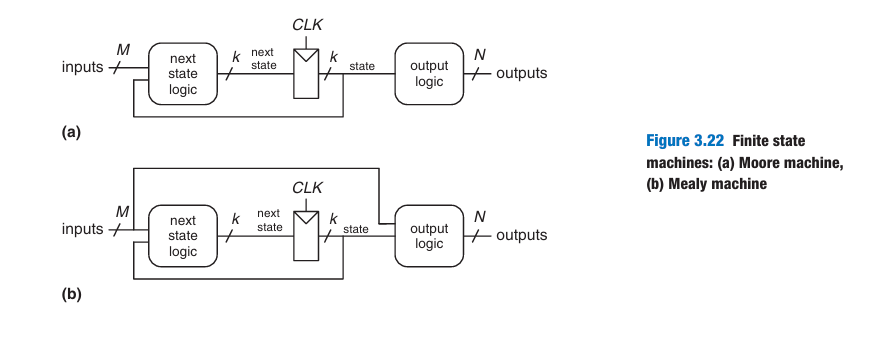

- 输入、输出:M个输入、N个输出、k位状态,还有1个时钟信号和1个复位信号

- 组成:寄存器、两个组合逻辑块:下一个状态逻辑和输出逻辑。

- 分类:

- Moore:输出取决于当前状态

- Mealy:输出取决于当前状态与当前输入

- 状态机的分解:将复杂的有限状态机分解为多个互相作用的较简单的状态机

时序规范

动态约束

同步时序电路驶入必须在时钟沿附近的建立和维持时间(合称孔径时间)内保持稳定。

- 孔径时间(P83): 时钟沿到来前,输入必须在建立时间内保持稳定;时钟沿后,输入必须至少在保持时间内保持稳定。因此孔径时间是输入保持稳定的时间总和。

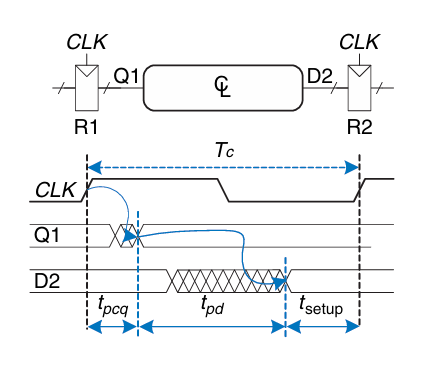

系统时序

- Tc是重复时钟信号的上升沿之间的时间。倒数fc = 1/Tc为时钟频率。

- 建立时间约束(最大延迟约束)

- tpd ⇐ Tc - (tpcq + tsetup)

- 取决于建立时间,限制两个寄存器之间组合逻辑的最大延迟

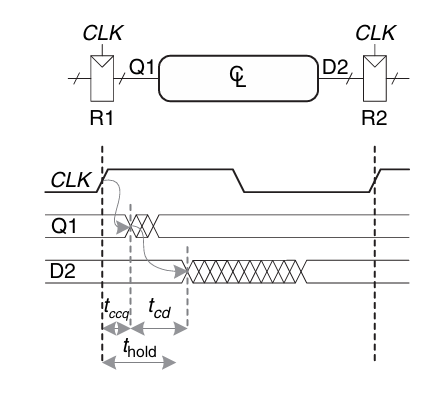

- 保持时间约束(最小延迟约束)

- tcd >= thold - tccq

- 可靠触发器满足thold ⇐ tccq,因此背靠背连结组成寄存器的时候不会导致问题。事实上,触发器经常被设计成thold = 0。但如果保持时间较长且当前不满足,可以尝试增加缓冲器。

- 限制两个寄存器之间,组合逻辑的最小延迟

亚稳态

- 定义:触发器对孔径时间内变化的输入采样时,输出可能区禁止区域内0~VDD之间的电压。

- 分辨时间:输入在孔径时间外,则tres = tpcq,否则比较长。在稳定到0或1前一直是一个亚稳定值,到稳态的时间无界。

同步器

为了确保产生正确的逻辑电平,所有异步输入必须经过同步器。