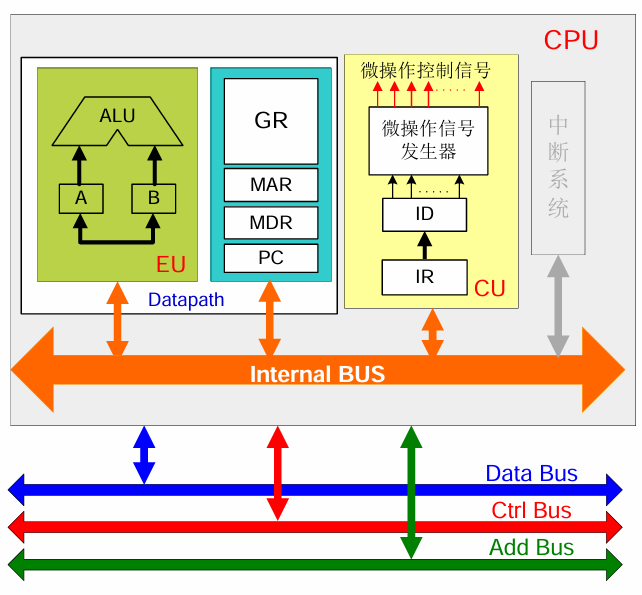

CPU 的组成

- 控制单元(控制器,Control)

- 指令地址部件:程序计数器 PC

- 指令寄存部件:指令寄存器 IR

- 译码部件:指令译码器 ID

- 时序部件:产生时序信号

- 控制信号生成部件

- 执行单元(数据通路,Datapath)

- 运算单元:ALU

- 寄存器单元:通用寄存器组(GPRs),标志寄存器(FR,又称程序状态字PSW),临时寄存器(TR)

CPU 性能指标

系统的速度可以用延迟和吞吐量度量。

概念 :

- 任务:经过处理后能产生输出的一组输入

- 延迟(响应时间):任务开始到结束所需的时间

- 吞吐量:系统单位时间内完成的任务量

- 指令平均执行时钟周期数(CPI):

- CPU 执行时间:

- 从响应时间中去除因等待I/O操作所花时间和CPU执行其他程序所花时间,是CPU真正花在运行一个程序上的时间。

- 这个是衡量性能的最重要的指标。

- 百万指令每秒(MIPS):

- 百万浮点数操作每秒 (MFLOPS):

Warning

MIPS 和 MFLOPS 除了和机器有关,也和 ISA、所用测试程序等有关,因此需要谨慎参考。不同 ISA 比较没有价值,不同测试程序测出来也可能不一样,没有比较价值。

影响因素

- 指令数

- CPI

- 时钟周期

MIPS CPU 设计

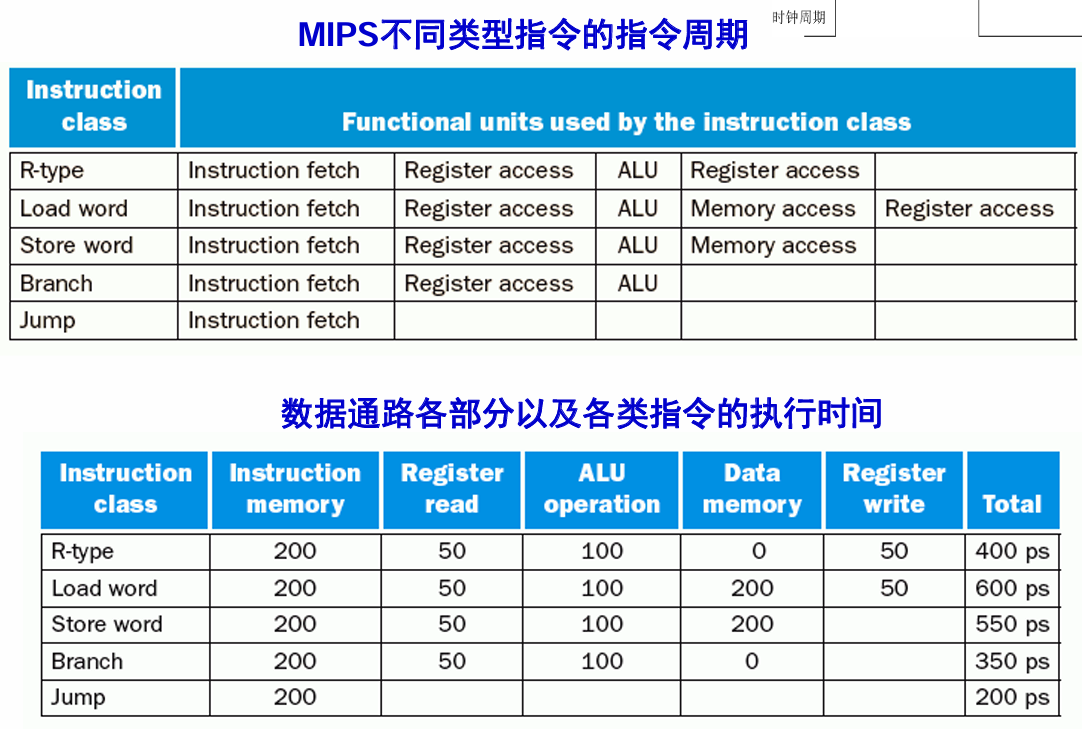

单周期

设计方案

性能分析

单周期 CPU 中,每条指令需要 1 个时钟周期,因此 CPI 为 1。

单周期 CPU 中,不同类型指令的耗时不同。而我们采取同步时序设计,时钟周期为常数,因此要足够长,满足最慢指令(lw 类指令)的耗时。

多周期

多周期 CPU 将指令执行过程分为多个较短步骤。每个步骤中,CPU 可以读写存储器或寄存器,或使用 ALU。不同指令使用的步骤数不同,即时钟周期数不同,因此简单指令比复杂指令可以更快。

因此多周期 CPU 的速度更快(虽然不总是这样),成本更低(因为复用元件)

性能分析

指令执行时间依赖于使用的周期数和周期时间。

- 采取同步时序设计,时钟周期为常数,因此要足够长,满足最慢步骤(读存储器)的耗时。

beq,j需要的周期最少,为 3;sw,addi等 I 型运算指令,R 型指令需要 4 周期;lw需要 5 周期。

因此 CPI 取决于使用指令的相对频度。

并行

- 并行:

- 空间并行:提供多个相同硬件,以便同时处理多个任务 (超标量)

- 时间并行:把一个任务分成多个阶段,每个时间内每部分都有一个不同任务正在处理,从而重叠处理任务(流水线)

- 效果:

- 延迟为 L 的任务,无并行则吞吐量为 1/L;

- 若空间并行系统中有 N 个硬件,则吞吐量为 N/L;

- 若时间并行系统中任务分步,最长延迟为 L’,则吞吐量为 L’/N。

- 依存关系:当前任务依赖于前一个任务的结果,则只有前一个任务完成后,后一个任务才能开始。

- 流水线 CPU 设计文档:

- P5 Design (五级流水线)

- P6 Design(支持乘除法)

- Final Design(支持中断、异常)